| □ H11年04月期 A-13 Code:[HD0801] : PLLの原理構成。ブロック図 |

検索サイトから来た方は… 無線工学の基礎 トップへ 以下をクリックすると、元のページが行き先に飛び、このウインドウは閉じます |

| ■ 無線工学を学ぶ |

|

(1) 無線工学の基礎 |

|

年度別出題一覧 |

| H11年 4月期,8月期,12月期 |

| H12年 4月期,8月期,12月期 |

| H13年 4月期,8月期,12月期 |

| H14年 4月期,8月期,12月期 |

| H15年 4月期,8月期,12月期 |

| H16年 4月期,8月期,12月期 |

| H17年 4月期,8月期,12月期 |

| H18年 4月期,8月期,12月期 |

| H19年 4月期,8月期,12月期 |

| H20年 4月期,8月期,12月期 |

| H21年 4月期,8月期,12月期 |

| H22年 4月期,8月期,12月期 |

| H23年 4月期,8月期,12月期 |

| H24年 4月期,8月期,12月期 |

| H25年 4月期,8月期,12月期 |

| H26年 4月期,8月期,12月期 |

| H27年 4月期,8月期,12月期 |

| H28年 4月期,8月期,12月期 |

| H29年 4月期,8月期,12月期 |

| H30年 4月期,8月期,12月期 |

| R01年 4月期,8月期,12月期 |

| R02年 4月期,9月期,12月期 |

| R03年 4月期,9月期,12月期 |

| R04年 4月期,8月期,12月期 |

| R05年 4月期,8月期,12月期 |

| R06年 4月期,8月期,12月期 |

|

分野別出題一覧 |

| A 電気物理, B 電気回路 |

| C 能動素子, D 電子回路 |

| E 送信機, F 受信機 |

| G 電源, H アンテナ&給電線 |

| I 電波伝搬, J 計測 |

| ■ サイトポリシー |

| ■ サイトマップ[1ama] |

| ■ リンクと資料 |

■ メールは下記まで |

|

| 2025年 |

| 03/31 R06/12月期問題頁掲載 |

| 03/31 R06/08月期問題頁掲載 |

| 03/31 R06/04月期問題頁掲載 |

| 03/31 R05/12月期問題頁掲載 |

| 03/31 R05/08月期問題頁掲載 |

| 03/31 R05/04月期問題頁掲載 |

|

|

| |||||||||||||||||||||

| |||||||||||||||||||||

| |||||||||||||||||||||

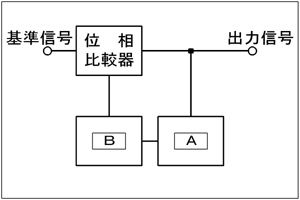

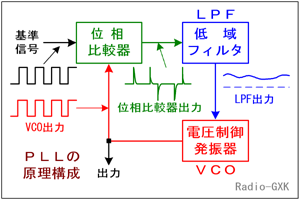

位相同期ループ(回路をやっているとPLLと呼ぶ方が普通ですね)はよく出題されます。この問題のようにPLL単体だけではなく、分周器と組み合わせて、任意の周波数を発生させられる周波数シンセサイザの問題も多いです。[1]PLLの構成1 位相比較器と低域フィルタ(LPF)Fig.HD0801_aは、単純化したPLLの構成です。実際に使われているものはもっと複雑ですが、要素だけ見れば大概このようになっています。 | |

|

まず、入力としては基準となる信号が必要です。普通は、基準として水晶発振子や特殊なところでは標準電波のキャリア(搬送波)など、周波数が一定で変動が少ないものを選びます。 基準入力と出力は、PLLのキー部分の一つである「位相比較器」に入ります。「位相」を「比較」するとはどういうことかというと、基準信号と出力の位相のズレに応じた(電圧)出力を得るというものです。 例えば、基準に対して出力の位相が進んでいればそのズレの大きさに応じた正の電圧を、遅れていれば負の電圧を出力します。 |

Fig.HD0801_a PLLの原理的構成と各部の波形 |

|

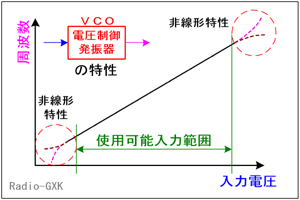

位相比較器の出力は「リアルタイム」で、信号の周期ごとに出力されますから、基準入力の周波数と同じ成分を多く含む脈流になっています。これでは、後に繋がる「電圧制御発振器(VCO)」の動作に都合が悪いので、低域フィルタ(これも単にLPFと言うのが普通です)に通し、電圧の変化を平坦にします。 PLL出力が入力の周波数に同期することを、「ロックする」と言います。入力の周波数が変化した場合、再びロックするまでにはある程度の時間がかかります。その時間は、主にLPFの時定数に依存します。 LPFの帯域を狭くする(時定数を長くする)と、VCO入力の変化の度合いが緩やかになるので、入力側で周波数を頻繁に変更する用途では、ロックアップタイム(PLLが所定の周波数にロックされるまでの時間)が長くなります。逆に帯域を広くすると、ロックアップタイムは短くなりますが、ロックが不安定になります。 [2]PLLの構成2 電圧制御発振器(VCO)LPFの出力を入力とする電圧制御発振器(Voltage Controlled Oscillator)は、左の図Fig.HD0801_bのように、入力の電圧に対して直線的に出力周波数が変化する領域を持った発振器です。普通、入力電圧が変化しても、出力振幅は変動しません。変化するのは周波数だけです。 | |

Fig.HD0801_b VCOの入出力特性 |

VCOの特性により、この直線的に使える範囲は様々です。通常、範囲外では非直線になるので使いませんが、(後に書くように)PLLは負帰還回路ですので、多少この特性が曲がっていても、ロックできないことはありません。 位相比較器の出力がLPFを経てVCOに入る時に、位相ズレに応じた電圧が、ズレを修正する方向にVCOの周波数を変動させるように設計します。Fig.HD0801_aを見てお気づきの方もおられるかもしれませんが、PLLは「帰還(フィードバック」回路、それも負帰還回路です。 |

基準信号に対して、出力の位相が遅れればVCOの周波数を上げ気味にして位相を進め、逆に出力の位相が進めばVCOの周波数を下げて位相を遅らせます。このようにして、出力周波数が、基準入力に対して位相も周波数も同じになるように制御するのがPLLです。(但し、この動作は基準信号の1周期内では行なえず、LPFの時定数にもよりますが、数十周期〜数千周期分程度の時間が必要です。)[3]PLLの使い方・用途今まで見てきたものは、出力として入力と同じ周波数でロックされるPLLですが、入力周波数f [Hz]に対して、整数n倍の周波数nf [Hz]を出力するPLLもあります。そのようなものは、VCOの出力と位相比較器の間にn分周器を入れて、位相比較器には同じ周波数fで入力されるようにします。このようにすれば、元の周波数に位相が合っているn倍の周波数が作り出せます。PLLの応用は非常に幅広く、ずれない周波数で運用する必要のある無線機はもちろんのこと、安定な回転数が必要なモーターの制御やCPUの内部の周波数逓倍にも使われています。特に、無線機やモーターで周波数や回転数を変えたりする必要がある場合には、上に述べたn倍の周波数を発生するPLLと外部の分周器(分周比m)とを組合せ、(n/m)fの安定な周波数を発生させる、周波数シンセサイザが利用されます。このような用途ではnやmをコンピュータ制御で設定します。 それでは、解答に移ります。 A…位相比較器の出力を入れるものですから低域フィルタです B…低域フィルタの出力は電圧制御発振器に入ります となりますから、正解は2と分かります。 | |

|

|