| □ H15年04月期 B-02 Code:[HC0402] : 高周波用及び一般のFETの説明文で、動作原理、構造の比較 |

検索サイトから来た方は… 無線工学の基礎 トップへ 以下をクリックすると、元のページが行き先に飛び、このウインドウは閉じます |

| ■ 無線工学を学ぶ |

|

(1) 無線工学の基礎 |

|

年度別出題一覧 |

| H11年 4月期,8月期,12月期 |

| H12年 4月期,8月期,12月期 |

| H13年 4月期,8月期,12月期 |

| H14年 4月期,8月期,12月期 |

| H15年 4月期,8月期,12月期 |

| H16年 4月期,8月期,12月期 |

| H17年 4月期,8月期,12月期 |

| H18年 4月期,8月期,12月期 |

| H19年 4月期,8月期,12月期 |

| H20年 4月期,8月期,12月期 |

| H21年 4月期,8月期,12月期 |

| H22年 4月期,8月期,12月期 |

| H23年 4月期,8月期,12月期 |

| H24年 4月期,8月期,12月期 |

| H25年 4月期,8月期,12月期 |

| H26年 4月期,8月期,12月期 |

| H27年 4月期,8月期,12月期 |

| H28年 4月期,8月期,12月期 |

| H29年 4月期,8月期,12月期 |

| H30年 4月期,8月期,12月期 |

| R01年 4月期,8月期,12月期 |

| R02年 4月期,9月期,12月期 |

| R03年 4月期,9月期,12月期 |

| R04年 4月期,8月期,12月期 |

| R05年 4月期,8月期,12月期 |

| R06年 4月期,8月期,12月期 |

|

分野別出題一覧 |

| A 電気物理, B 電気回路 |

| C 能動素子, D 電子回路 |

| E 送信機, F 受信機 |

| G 電源, H アンテナ&給電線 |

| I 電波伝搬, J 計測 |

| ■ サイトポリシー |

| ■ サイトマップ[1ama] |

| ■ リンクと資料 |

■ メールは下記まで |

|

| 2025年 |

| 03/31 R06/12月期問題頁掲載 |

| 03/31 R06/08月期問題頁掲載 |

| 03/31 R06/04月期問題頁掲載 |

| 03/31 R05/12月期問題頁掲載 |

| 03/31 R05/08月期問題頁掲載 |

| 03/31 R05/04月期問題頁掲載 |

|

|

| |||||||||||||||||||||

| |||||||||||||||||||||

| |||||||||||||||||||||

電界効果トランジスタ(以下、単にFETと記します。単にトランジスタと記した時は、バイポーラトランジスタの意味です)の構造や動作を問う問題は、非常によく出題されています。ここでは、特に高周波増幅に注目して見て行きます。[1]FETはバイポーラトランジスタとどう違う?バイポーラトランジスタは、ベースに流れる電流の一定倍の電流がコレクタに流れる、という現象を利用して、電流で電流を制御する素子、でした。一方、FETでは、ゲートという制御電極にかける電圧で、ドレインとソースという電極間にできた「チャネル」という電流の流れ道の幅を電気的に変化させて、電流を制御する構造になっています。つまり、電圧で電流を制御する素子です。 別の観点では、トランジスタではベース−エミッタ間に順電流を流しますので、ここで電子と正孔(ホール)の再結合が生じますが、FETではそれがありません。電流の担い手が、電子(NチャネルFETの場合)または正孔(PチャネルFETの場合)のどちらかです。このため、バイポーラトランジスタに対してFETは「ユニポーラ素子」と言うことがあります。「バイ」は2つの、という意味で、電子と正孔を言っており、「ユニ」は一つの、という意味で、電子のみ、または正孔のみを意味します。 [2]FETにはどんな種類がある?まず、構造に入る前に、バイポーラトランジスタにNPNやPNPといった種類があるように、FETにも種類があるので、確認しておきます。 | |

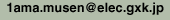

(1) 構造による分類後で出てきますが、FETはその構造により「接合形」と「MOS形」に分けられます。接合形は制御電極(ゲート)と、チャネルが、それぞれP形・N形の半導体でできており、それらが直接接合された構造のものです。一方、MOS形は、ゲートとチャネルの間に酸化物膜を挟んだ構造のものです。 (2) 特性による分類 |

Fig.HC0402_a FETの種類と回路図記号 |

ゲートにかかる電圧が0 [V]でもチャネルに電流が流せるFETを、デプレッション形、一定方向の電圧をかけないと電流が流せないものをエンハンスメント形、といいます(これについては後で詳しく見ます)。(3) チャネルを構成する半導体による分類チャネルを流れる電流の担い手が、電子であるものをNチャネルFET、正孔(ホール)であるFETをPチャネルFETといいます。改めて、電極の名前と働きの対応はいいでしょうか? ドレインとソースはそれぞれチャネルの入り口と出口です。ゲートは、チャネルに流れる電流を制御する端子です。 Fig.HC0402_aには、バイポーラにはデプレッション形とエンハンスメント形の区別がないことになっていますが、ある本ではあるそうです。個人的にはエンハンスメント形があるのを見たことがない(普通、接合形ではゲートとチャネル間の電圧がゼロでも電流は流れる)ので、ここではあえて書いていません。 [3]FETは「電圧で電流を制御」する素子モノの本にはよくこう書いてある(上にも知ったような顔をして書きました)のですが、イマイチイメージがピンと来ない方、おられるかもしれません。正確な記述は半導体物理の本に出ていますが、ここではイメージを掴むために、正確さは置いておいて、大雑把に書いてみます。 | |

|

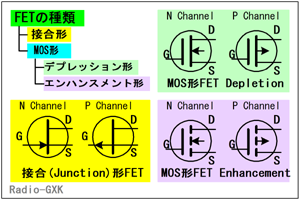

ここでは電流の運び手が電子(多数キャリア)であるNチャネル形のFETを見てみましょう(Pチャネル形も電流・電圧の向きが逆で、多数キャリアがホールなだけで、原理は全く同じです)。 まず、接合形FETはFig.HC0402_b左のような構造になっています。N形のチャネルに、P形のゲートがPN接合しており、チャネルとゲート間には逆バイアスがかかるようにして使用します。電流はチャネルを流れます。 逆バイアスがかかっていますから、ゲートに電流は流れません(正確には漏れ電流程度の微小電流が流れます)。 |

Fig.HC0402_b FETの構造 |

|

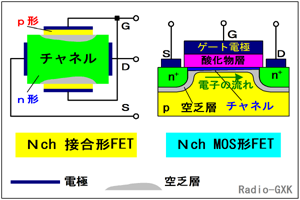

また、接合部(MOS形では酸化物層の下)に空乏層ができていて、これが電流を制限します。逆バイアスをどんどん大きくして行くと、しまいには上下の空乏層がくっついてしまいます。この状態を「ピンチオフ」といいます。しかし不思議なことに、これで電流が全く流れなくなってしまうわけではなく、空乏層の中をある程度の電流が流れます。 その空乏層は、ソースとドレインでは、ドレインの方が高電圧、ゲートとチャネルではゲートの方が低電圧(逆バイアス)ですから、空乏層の厚さは場所によって異なり、ゲートの下でドレインに近い側が厚く、ソースに近い側が薄くなります。 一方、MOS FETの方は似ていますが少し構造が違います。最も違いが大きいのは、ゲートの電極の下に酸化物層(通常はSiO2)があることです。接合形FETではゲートに漏れ電流程度の電流が流れますが、MOS形では、この絶縁層のためにPN接合の漏れ電流すらも流れません。入力インピーダンスが極めて高い特徴があります。 電流が流れるチャネルは、ちょっと変わっていて、ゲートの直下にできる「反転層」というものが電流の通り道になります。ゲートに逆バイアスをかけると、チャネルを構成しているP形半導体の少数キャリアである電子がゲートの下に寄ってきて、ホールよりも電子の多い、逆転層を作り出します。ここが電流の通路(チャネル)になります。この逆転層の厚さがゲート電圧によって変化するため、電圧で電流が制御できる、というわけです。 [4]高周波増幅向きのGaAs FETとは?シリコンではなく、ガリウムと砒素の化合物を材料とする半導体です。通称「ガリ砒素」と呼ばれています。このような異種の元素からできた半導体を、化合物半導体といいます。この化合物内での電子やホールの移動速度が、シリコンに比べて数倍から10倍程度大きいので、高速動作が可能です。加えて、低雑音である、ということも利点です。じゃあ、ガリ砒素でCPUを作れば、超高速のパソコンができるんじゃないか…なんて雑談ですが。ガリ砒素基板自体のコストが非常に高いことと、加工や微細パターン描画などの製造技術がシリコンより困難なこともあって、多分今と同じCPUは無理でしょう。ガリ砒素のMOS構造なんて聞いたこともないので、消費電力も低くはできないでしょう。 でも、衛星放送を小さなパラボラアンテナで受信したり、430MHzでEMEをやろう、なんていうと、俄然存在意義が出てきて、必ずと言っていいほど、このガリ砒素FETが高周波増幅段に使われます。また、熱にも強いので、携帯の基地局などのハイパワーアンプにも用いられます。 [5]デュアルゲートFETの動作とは?高周波用FETの一部には、ゲートが2つあるものがあります。一般的な使い方としては、第1ゲートを信号入力に、第2ゲートを交流的に接地して使います。 | |

|

もう少し具体的に書くと、Fig.HC0402_cの左のようになります。負荷抵抗はドレインに繋ぎます。 すると、この回路はあたかもソース接地回路とゲート接地回路がシリーズに繋がったような回路(Fig.HC0402右)として動作し、高周波増幅回路としては「いいとこ取り」をしたようなものになります。 では、何が「いいとこ」なのかを見て行きましょう。 予備知識として必要なのは、トランジスタ増幅での各接地方式と周波数特性、入力インピーダンス等の関係と、端子間容量の存在です。 |

Fig.HC0402_c デュアルゲートFET回路 |

|

FETもトランジスタと同様(順序が逆になりますが、FETの接地方式と増幅動作については次の項を参照して下さい)に、Fig.HC0402_c右において示したように、電極間に容量が存在し、出力が逆位相で、振幅がn倍である時に、この電極間容量(特にゲート−ドレイン間)が(n+1)倍に見える「ミラー効果」が存在することも同じです。 Tr1はソース接地のゲイン1のアンプとして、Tr2はゲート接地のアンプとして動作します。こうすると、Tr1ではミラー効果は起こりますが(ゲインが小さいので)その影響は小さく、また、Tr2では、ゲートが接地されているので、ミラー効果は起こりません。 Tr1では電圧利得は取れませんが、出力インピーダンスが低いので、次段のゲート接地の入力インピーダンスの低さも問題とならず、Tr2で緩衝増幅して負荷抵抗RLでの電圧利得が稼げます。つまり、2段で巧みにミラー効果を避けながら、高周波まで増幅が可能になる、という構成です。このような接続方法を、カスケード接続といいます。 [6]FETの接地方式と増幅動作トランジスタと同じ、とは書いたものの、FETでのそれぞれの接地方式には、以下のようになります。記号はMOS FETで書いていますが、接合形でも原理は同じです。 | |

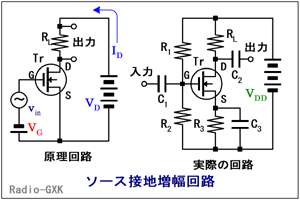

Fig.HC0402_d ソース接地回路の構成 |

(1) ソース接地ソース接地回路はトランジスタ回路で言う、エミッタ接地とほぼ同じです。負荷抵抗RLを大きく取って、電圧利得を大きくすると、ミラー効果が大きくなりますので、他の接地方式と比べて、周波数特性はあまり良くはなりません。出力インピーダンスは負荷抵抗と同じになるので、これまた負荷抵抗はあまり大きくできません。入出力の位相が逆になるのも電圧利得が1より大きく取れるのもエミッタ接地と同じです。一方、入力インピーダンスはトランジスタと違い、FETの特性で決まりますので、高くなります。 |

Fig.HC0402_dの左はバイアス回路などを除いた原理図ですが、実際の回路では同図右側のように設計します。ソースは交流的に接地ですが、C3がその役割を果たします。(2) ドレイン接地(ソースフォロワ)ドレイン接地回路は、ソースフォロワと言った方がなじみが深いかもしれません。 | |

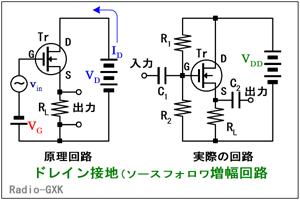

Fig.HC0402_e ドレイン接地回路の構成 |

トランジスタ回路で言う、エミッタフォロワとほぼ同じ動作をします。ミラー効果が無視できるので、周波数特性は良好ですが、ソース接地と同様、出力インピーダンスは負荷抵抗と同じになるので、これまた負荷抵抗はあまり大きくできません。電圧利得の上限は出力インピーダンスの条件と電圧振幅が取れるかどうかで決まります。入出力の位相は同相です。 また、図からわかるように、ゲートよりも電位が低いので、電圧利得は1より小さくなります。 入力インピーダンスは、元々FETのゲートに入力するので高く取れます。緩衝増幅器(バッファ)として主に用いられます。 |

Fig.HC0402_eの左は原理図、です。実際の回路では同図右側のように設計します。ドレインは交流的に接地ですが、電源に接続されている、ということは電位的には一定(交流的に接地)ですので、その役割を果たします。(3) ゲート接地 | |

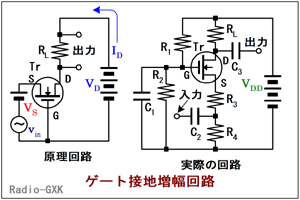

Fig.HC0402_f ゲート接地回路の構成 |

ゲート接地回路は、トランジスタ回路で言うベース接地回路に当たります。他の2つと異なり、電流が流れるソースに入力しますので、入力インピーダンスは低くなります。 また、ゲートが交流的に接地されているので、ミラー効果は原理的に発生せず、周波数特性は良好です。負荷抵抗RLを大きくすることで、電圧利得を大きくすることができます。 Fig.HC0402_f左が原理図です。実際の回路では同図右側のように設計します。ゲートは交流的に接地ですが、C1がその役割を果たします。 |

|

このように、FETにもトランジスタと同様に接地方式により特性が異なりますので、上に述べたような、デュアルゲートFETのように、ソース接地とゲート接地を組み合わせて使えば、周波数特性がよく、かつ、電圧利得もそこそこ取れる、というアンプが構成できます。 それでは、解答に移ります。 ア…FETは1ユニポーラトランジスタです イ…金属M-酸化膜O-半導体Sは9MOS形FETです ウ…ゲートを2つ持つFETは5デュアルゲートFETです エ…問題文のように接続すると、6カスケード接続と等価です オ…電子の移動度が大きい化合物半導体は8ガリウムひ素FETです となります。 | |

|

|