| □ H20年04月期 B-02 Code:[HC0401] : FETの説明文で、動作原理、接合形とMOS形の比較、GaAsの特性等 |

検索サイトから来た方は… 無線工学の基礎 トップへ 以下をクリックすると、元のページが行き先に飛び、このウインドウは閉じます |

| ■ 無線工学を学ぶ |

|

(1) 無線工学の基礎 |

|

年度別出題一覧 |

| H11年 4月期,8月期,12月期 |

| H12年 4月期,8月期,12月期 |

| H13年 4月期,8月期,12月期 |

| H14年 4月期,8月期,12月期 |

| H15年 4月期,8月期,12月期 |

| H16年 4月期,8月期,12月期 |

| H17年 4月期,8月期,12月期 |

| H18年 4月期,8月期,12月期 |

| H19年 4月期,8月期,12月期 |

| H20年 4月期,8月期,12月期 |

| H21年 4月期,8月期,12月期 |

| H22年 4月期,8月期,12月期 |

| H23年 4月期,8月期,12月期 |

| H24年 4月期,8月期,12月期 |

| H25年 4月期,8月期,12月期 |

| H26年 4月期,8月期,12月期 |

| H27年 4月期,8月期,12月期 |

| H28年 4月期,8月期,12月期 |

| H29年 4月期,8月期,12月期 |

| H30年 4月期,8月期,12月期 |

| R01年 4月期,8月期,12月期 |

| R02年 4月期,9月期,12月期 |

| R03年 4月期,9月期,12月期 |

| R04年 4月期,8月期,12月期 |

| R05年 4月期,8月期,12月期 |

| R06年 4月期,8月期,12月期 |

|

分野別出題一覧 |

| A 電気物理, B 電気回路 |

| C 能動素子, D 電子回路 |

| E 送信機, F 受信機 |

| G 電源, H アンテナ&給電線 |

| I 電波伝搬, J 計測 |

| ■ サイトポリシー |

| ■ サイトマップ[1ama] |

| ■ リンクと資料 |

■ メールは下記まで |

|

| 2025年 |

| 03/31 R06/12月期問題頁掲載 |

| 03/31 R06/08月期問題頁掲載 |

| 03/31 R06/04月期問題頁掲載 |

| 03/31 R05/12月期問題頁掲載 |

| 03/31 R05/08月期問題頁掲載 |

| 03/31 R05/04月期問題頁掲載 |

|

|

| |||||||||||

| |||||||||||

| |||||||||||

電界効果トランジスタ(以下、単にFETと記します)の構造や動作を問う問題は、非常によく出題されています。それだけ電子機器にはよく使われている(これを使っていない機器はまずないでしょう)ということですので、少し詳しく見て行きます。[1]FETはバイポーラトランジスタとどう違う?バイポーラトランジスタは、ベースに流れる電流の一定倍の電流がコレクタに流れる、という現象を利用して、電流で電流を制御する素子、でした。一方、FETでは、ゲートという制御電極にかける電圧で、ドレインとソースという電極間にできた「チャネル」という電流の流れ道の幅を電気的に変化させて、電流を制御する構造になっています。つまり、電圧で電流を制御する素子です。 別の観点では、トランジスタではベース−エミッタ間に順電流を流しますので、ここで電子と正孔(ホール)の再結合が生じますが、FETではそれがありません。電流の担い手が、電子(NチャネルFETの場合)または正孔(PチャネルFETの場合)のどちらかです。このため、バイポーラトランジスタに対してFETは「ユニポーラ素子」と言うことがあります。「バイ」は2つの、という意味で、電子と正孔を言っており、「ユニ」は一つの、という意味で、電子のみ、または正孔のみを意味します。 [2]FETにはどんな種類がある?まず、構造に入る前に、バイポーラトランジスタにNPNやPNPといった種類があるように、FETにも種類があるので、確認しておきます。 | |

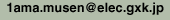

(1) 構造による分類後で出てきますが、FETはその構造により「接合形」と「MOS形」に分けられます。接合形は制御電極(ゲート)と、チャネルが、それぞれP形・N形の半導体でできており、それらが直接接合された構造のものです。一方、MOS形は、ゲートとチャネルの間に酸化物膜を挟んだ構造のものです。 (2) 特性による分類 |

Fig.HC0401_a FETの種類と回路図記号 |

ゲートにかかる電圧が0 [V]でもチャネルに電流が流せるFETを、デプレッション形、一定方向の電圧をかけないと電流が流せないものをエンハンスメント形、といいます(これについては後で詳しく見ます)。(3) チャネルを構成する半導体による分類チャネルを流れる電流の担い手が、電子であるものをNチャネルFET、正孔(ホール)であるFETをPチャネルFETといいます。改めて、電極の名前と働きの対応はいいでしょうか? ドレインとソースはそれぞれチャネルの入り口と出口です。ゲートは、チャネルに流れる電流を制御する端子です。 Fig.HC0401_aには、接合形FETにはデプレッション形とエンハンスメント形の区別がないことになっていますが、ある本ではあるそうです。個人的にはエンハンスメント形があるのを見たことがない(普通、接合形ではゲートとチャネル間の電圧がゼロでも電流は流れる)ので、ここではあえて書いていません。 [3]FETは「電圧で電流を制御」する素子モノの本にはよくこう書いてある(上にも知ったような顔をして書きました)のですが、イマイチイメージがピンと来ない方、おられるかもしれません。正確な記述は半導体物理の本に出ていますが、ここではイメージを掴むために、正確さは置いておいて、大雑把に書いてみます。 | |

|

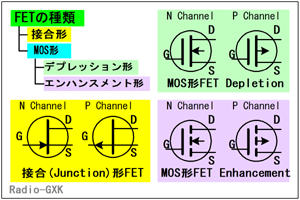

ここでは電流の運び手が電子(多数キャリア)であるNチャネル形のFETを見てみましょう(Pチャネル形も電流・電圧の向きが逆で、多数キャリアがホールなだけで、原理は全く同じです)。 まず、接合形FETはFig.HC0401_b左のような構造になっています。N形のチャネルに、P形のゲートがPN接合しており、チャネルとゲート間には逆バイアスがかかるようにして使用します。電流はチャネルを流れます。 逆バイアスがかかっていますから、ゲートに電流は流れません(正確には漏れ電流程度の微小電流が流れます)。 |

Fig.HC0401_b FETの構造 |

|

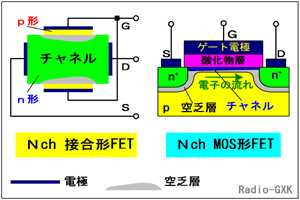

また、接合部(MOS形では酸化物層の下)に空乏層ができていて、これが電流を制限します。逆バイアスをどんどん大きくして行くと、しまいには上下の空乏層がくっついてしまいます。この状態を「ピンチオフ」といいます。しかし不思議なことに、これで電流が全く流れなくなってしまうわけではなく、空乏層の中をある程度の電流が流れます。 その空乏層は、ソースとドレインでは、ドレインの方が高電圧、ゲートとチャネルではゲートの方が低電圧(逆バイアス)ですから、空乏層の厚さは場所によって異なり、ゲートの下でドレインに近い側が厚く、ソースに近い側が薄くなります。 一方、MOS FETの方は似ていますが少し構造が違います。最も違いが大きいのは、ゲートの電極の下に酸化物層(通常はSiO2)があることです。接合形FETではゲートに漏れ電流程度の電流が流れますが、MOS形では、この絶縁層のためにPN接合の漏れ電流すらも流れません。入力インピーダンスが極めて高い特徴があります。 あまりにインピーダンスが高いため、ゲートピンを手で触れたりすると、静電気で絶縁層が破壊されます。この破壊は、ゲートとチャネル間に掛かる電圧が原因なので、取扱の際にはソース(又はドレイン)とゲートを短絡しておくと良いとされます。 電流が流れるチャネルは、ちょっと変わっていて、ゲートの直下にできる「反転層」というものが電流の通り道になります。ゲートに逆バイアスをかけると、チャネルを構成しているP形半導体の少数キャリアである電子がゲートの下に寄ってきて、ホールよりも電子の多い、逆転層を作り出します。ここが電流の通路(チャネル)になります。この逆転層の厚さがゲート電圧によって変化するため、電圧で電流が制御できる、というわけです。 [4]電圧に伴ってMOS FETの動作はどう変化するか次に、Fig.HC0401_cのようにMOS FETをソース接地(コモン)で接続し、ゲート電圧とドレイン電圧をいろいろ変化させて、その動作を見てみましょう。 | |

Fig.HC0401_c MOS FETの線形領域での動作 |

(1) ゲート電圧が低い時ドレイン−ソース間電圧VDSがゲート電圧に比べて十分低い時は、基板であるP形の中に空乏層はできますが、その厚さは薄く、またチャネルはD-S間を途切れることなく繋いでいます。チャネルの厚さは、ゲート電圧が上がれば上がるほど厚くなりますので、流れる電流も多くなります。逆に、ゲート電圧がある一定値だとすると、チャネルがD-S間を繋いでいる限りは、そこを流れる電流はVDSに比例します。 |

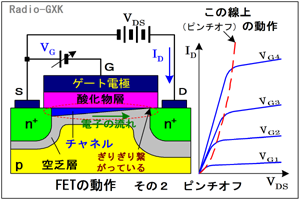

つまり、FETがゲート電圧をパラメータにVDSに比例した電流が流れる抵抗のように振舞うので、ここを「線形領域」と呼びます。ちなみに、(バイポーラ)トランジスタでいう、線形領域とは概念が全く異なりますので、注意して下さい。(2) ピンチオフが生じている状態 | |

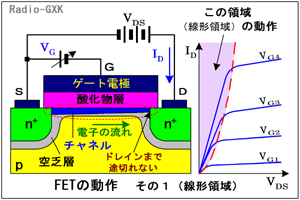

Fig.HC0401_d MOS FETのピンチオフ状態 |

引き続き、ゲート電圧を一定に保ちながらVDSを上げてゆくと、空乏層が厚くなり、ドレインの手前でチャネルが切れかかります。この状態を「ピンチオフ」といいます。 この、線形領域から(後に書く)飽和領域に遷移する電圧をピンチオフ電圧といい、ちょうどチャネルがドレインの手前で、薄くなって切れ掛かっている状態を示しています。ここから、今までVDSに対しては、抵抗のように振舞っていたFETが、様相を変え始めます。 ピンチオフが起こる電圧は一定ではなく、Fig.HC0401_dの右にあるように、ゲート電圧とVDSの両方の値に依存します。 |

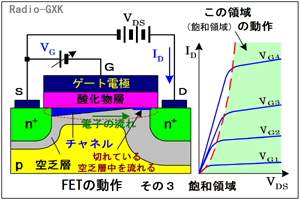

(3) ドレイン−ソース間電圧が十分大きい時 | |

Fig.HC0401_e MOS FETの飽和領域での動作 |

VDSがさらに大きくなると、空乏層が厚くなるとともに、チャネルが途中で切れてしまいます。チャネルが切れてしまうこと=電流が流れなくなること、ではなくて、先に述べたように、電子は空乏層の中を、ドレインにかかっている正電圧に引かれて移動します。但し、その量は(線形領域での振舞いと異なり)VDSを上昇させてもあまり増えません。 この領域のことを、「飽和領域」といい、通常FETで増幅器を組む時はこの領域の動作を利用します。 |

|

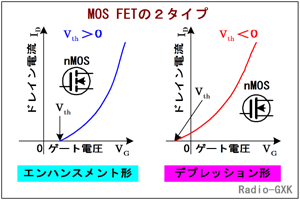

この領域では、Fig.HC0401_eの右のグラフのように、ドレイン電流はVDSに対してはあまり変化しませんが、ゲート電圧に対しては大きく変化します。つまり、ここでも、ゲート電圧でドレイン電流を制御していることになるわけです。 ここでまた注意点ですが、ここでの「飽和」という言葉は、バイポーラトランジスタの飽和と異なります。 [5]エンハンスメント形とデプレッション形上にも少し書きましたが、FETにはエンハンスメント形とデプレッション形があります。これらの違いは、ゲートに電圧がかかっていない(コモンに落ちている)時でもチャンネルが存在するかどうか、ということです。 | |

|

Fig.HC0401_fのように、ドレイン電流が流れ始めるゲート電圧が負でも、つまり逆バイアスをかけて使うべきゲートに、順バイアスをかけてもゲート電流が流れるものをデプレッション形、逆バイアスもある電圧Vthに達しないと流れないものエンハンスメント形、といいます。 FETをスイッチの代わりに使おうという場合は、ゲート電圧をかけていないのに電流が流れてしまっては都合が悪い(電流を切るのに負電源が必要)ですから、エンハンスメント形を使います。 原理からして、接合形FETでは、ゲートに電圧をかけなくてもチャネルが存在していますから、デプレッション形で、MOS形ではプロセスの工夫で両方作れます。 |

Fig.HC0401_f FETの2種類の特性 |

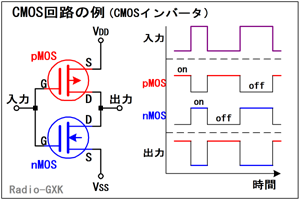

モータやインバータなど、MOS FETを電力制御に使う用途が近年非常に増えています。これらの回路では、普通、ゲートに電圧をかけて初めて電流が流れるエンハンスメント形を使用します。[6]CMOSロジックとは?FETをスイッチとして使う用途で、もう一つ忘れてはならないのが、CMOSロジック回路です。CMOSと書きますが、nMOSやpMOSのような区別ではなくて、nMOSとpMOSを組み合わせた回路をいいます(ちなみにCMOSはアナログ回路でも用いられるようになって来ましたが、圧倒的に数の多いロジック回路を取り上げます)。 | |

Fig.HC0401_g CMOSロジックの構成例 |

CMOSロジック(ここではNOT回路)の構造は、単純に描けばFig.HC0401_g左のようになっています。動作は簡単で、入力にHが入っている時は、上側のpMOSがOFFに、下側のnMOSがONになるので、出力にはLが、入力にLが入っている時は、上側のpMOSがONに、下側のnMOSがOFFになるので、出力にはHが出ます。 スイッチが直列に2個入っていて、入力に応じて交互にON-OFFするようになっている回路があって、両スイッチの接続されたノードから出力を取り出していると考えればよいでしょう。 |

|

この回路の特徴は、消費電力が小さいことです。MOSですから、入力から電流はほとんど流れません。また、両方のスイッチが同時にOFF(出力が不定になってしまう)やON(電源とGND間がショートしてしまう)になることはありません(細かいことを言うと、高速動作では、素子の過渡特性により、両方がONしてしまう瞬間があって、「貫通電流」というショート電流が流れます)。 このため、小規模なロジック回路から、パソコンのCPU等の超LSIに至るまで、論理回路は特殊な用途を除いてほとんどCMOSプロセスで作られています。製造コストが安いのも特徴です。直流に近い周波数ではほとんど電力を食いませんので、電池式の時計や電卓には昔から使われてきました。 「でも、パソコンのCPUはものすごく発熱するよ。あれで低消費電力なんて言えるの?」とお考えになるかもしれません。実は、CMOSといえども中身はMOSトランジスタ、すなわち逆バイアスのかかった空乏層を持つトランジスタです。逆バイアスされた空乏層は、可変容量ダイオードのところでも学ぶように、コンデンサです。コンデンサには低周波はほとんど流れませんが、高周波ほど流れやすくなります。 近頃のPCは、ギガヘルツオーダーのクロックが内部で飛び交っているので、CMOSといえどもゲートに大きな電流が流れてしまうため、もはや低消費電力ではないのです。また、プロセスルールが微細化しすぎて、極薄の絶縁体を飛び越えて電流が流れてしまう(トンネル効果)漏れ電流も消費電力を底上げしている一因です。さらに、集積度が極端に上がっているのも、発熱の密度という点では不利です。ですから、昔のPentuimは配線密度は低い、周波数も低い、でしたから、小さな放熱器でも動作させられました。 [7]GaAs FETとは?シリコンではなく、ガリウムと砒素の化合物を材料とする半導体です。通称「ガリ砒素」と呼ばれています。このような異種の元素からできた半導体を、化合物半導体といいます。この化合物内での電子やホールの移動速度が、シリコンに比べて数倍から10倍程度大きいので、高速動作が可能です。加えて、低雑音である、ということも利点です。じゃあ、ガリ砒素でCPUを作れば、超高速のパソコンができるんじゃないか…なんて雑談ですが。ガリ砒素基板自体のコストが非常に高いことと、加工や微細パターン描画などの製造技術がシリコンより困難なこともあって、多分今と同じCPUは無理でしょう。ガリ砒素のMOS構造なんて聞いたこともないので、消費電力も低くはできないでしょう。 でも、衛星放送を小さなパラボラアンテナで受信したり、430MHzでEMEをやろう、なんていうと、俄然存在意義が出てきて、必ずと言っていいほど、このガリ砒素FETが高周波増幅段に使われます。また、熱にも強いので、携帯の基地局などのハイパワーアンプにも用いられます。 [8]パワー系MOSFETの並列接続パワー系の回路(MOSFETをスイッチング素子として使うパワエレ回路)では、大電流に対応するため、複数のMOSFETを並列にして使うことがあります。バイポーラトランジスタでは、単純に並列運転すると、VBEのバラツキにより、特定のトランジスタに電流が集中するため、エミッタに直列に小さな抵抗を入れて、エミッタ電流が増えたら抵抗両端に発生する電圧が上がり、VBEが減少して負帰還が掛かるようにします。このような抵抗を入れる必要がない最近のMOSFETではバイポーラトランジスタよりは並列運転は容易だと言えますが、スイッチングに伴うスパイクノイズが他のMOSFETに混入して発振状態を引き起こすことがあるので、何でもかんでも並列OKというわけには行かないことには注意が必要です。 それでは、解答に移ります。 ア…キャリアが1種類のFETは1ユニポーラトランジスタです イ…金属-酸化膜-半導体構造は、FETの中で5MOS形FETです ウ…選択肢中の化合物半導体は8GaAs(ガリウムひ素)のみです エ…ガリ砒素は電子移動度がシリコンに比べ非常に7大きくなっています オ…ガリ砒素が優れているのは4高周波特性です となります。 | |

|

|