| □ H20年08月期 A-25 Code:[HJ0802] : デジタル電圧計の動作とA/Dコンバータの動作原理・特徴 |

検索サイトから来た方は… 無線工学の基礎 トップへ 以下をクリックすると、元のページが行き先に飛び、このウインドウは閉じます |

| ■ 無線工学を学ぶ |

|

(1) 無線工学の基礎 |

|

年度別出題一覧 |

| H11年 4月期,8月期,12月期 |

| H12年 4月期,8月期,12月期 |

| H13年 4月期,8月期,12月期 |

| H14年 4月期,8月期,12月期 |

| H15年 4月期,8月期,12月期 |

| H16年 4月期,8月期,12月期 |

| H17年 4月期,8月期,12月期 |

| H18年 4月期,8月期,12月期 |

| H19年 4月期,8月期,12月期 |

| H20年 4月期,8月期,12月期 |

| H21年 4月期,8月期,12月期 |

| H22年 4月期,8月期,12月期 |

| H23年 4月期,8月期,12月期 |

| H24年 4月期,8月期,12月期 |

| H25年 4月期,8月期,12月期 |

| H26年 4月期,8月期,12月期 |

| H27年 4月期,8月期,12月期 |

| H28年 4月期,8月期,12月期 |

| H29年 4月期,8月期,12月期 |

| H30年 4月期,8月期,12月期 |

| R01年 4月期,8月期,12月期 |

| R02年 4月期,9月期,12月期 |

| R03年 4月期,9月期,12月期 |

| R04年 4月期,8月期,12月期 |

| R05年 4月期,8月期,12月期 |

| R06年 4月期,8月期,12月期 |

|

分野別出題一覧 |

| A 電気物理, B 電気回路 |

| C 能動素子, D 電子回路 |

| E 送信機, F 受信機 |

| G 電源, H アンテナ&給電線 |

| I 電波伝搬, J 計測 |

| ■ サイトポリシー |

| ■ サイトマップ[1ama] |

| ■ リンクと資料 |

■ メールは下記まで |

|

| 2025年 |

| 03/31 R06/12月期問題頁掲載 |

| 03/31 R06/08月期問題頁掲載 |

| 03/31 R06/04月期問題頁掲載 |

| 03/31 R05/12月期問題頁掲載 |

| 03/31 R05/08月期問題頁掲載 |

| 03/31 R05/04月期問題頁掲載 |

|

|

| |||||||||||||||||||||

| |||||||||||||||||||||

| |||||||||||||||||||||

|

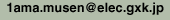

昔は針式のテスターでしたが、今では数字の出るマルチメータが普及してきました。そんなデジタル計測器の中でも、基本的な電圧計について、A/D変換の方式と絡めて問われています。 (問題ではA-D変換と書かれていますがAD変換とも書く人もいて、定まった表記はないようです。ここでは、「A/D変換」で統一します。) [1]A/D変換のキーワード1 「振幅量子化」我々が測定しようとする実世界の電圧や電流の値は、ほとんど全てがアナログ値です。それを、「針」ではなく、デジタルの「数字」で表示しようとすれば、そこに何らかの変換が必要です。ここでいうデジタルの数値は、1と0の2つの値を何桁も連ねて表記するものです。例えば、132.6 [mV]というアナログ電圧があったとして、これを10 [mV]を単位として表せば、1101(13を2進数表記したもの)という4桁の2進数で表せますが、もう少し桁を増やして、1 [mV]を単位とすれば、10000101(133を2進数表記したもの)と8桁が必要となります。この2進数の桁のことを「ビット(bit)」といい、132.6 [mV]は10 [mV]単位であれば4ビットで表記できますが、1 [mV]単位とすれば、8ビットが必要、ということになります。この1ビットあたりの電圧(あるいは全ビット数)を「分解能」といい、どこまで細かくデジタル化できるか、の指標となります。 お気づきになられたかもしれませんが、10 [mV]を「単位として」変換した時には、10より小さい2.6 [mV]分は切り捨てられていました。同様に、1 [mV]を単位として変換した時には、0.4 [mV]分が四捨五入で加えられたことになります。 この、デジタルの値とアナログの値の差のことを「量子化誤差」といい、お察しの通り、分解能が高く(ビット数が多く)なればなるほど、この誤差は小さくなりますが、扱うデータ量が増大します。ちなみに、この、振幅をある値を単位として丸めることを「振幅量子化(又は単に量子化)」といいます。普通のCDの音は、16ビットで量子化されています。 [2]A/D変換のキーワード2 「サンプリング周波数(周期)」一方、信号は時間とともに変化しますから、この振幅量子化(サンプリング)を一定間隔の時間で何度も行なって、データを記録して行けば、信号の波形が記録できます。この変換を行う時間間隔をサンプリング周期といいます。サンプリング周期の逆数はサンプリング周波数です。高速に変換できるコンバータであるほど、周期を短く(周波数は高く)できます。ちなみに、CDのサンプリング周波数は44.1 [kHz]で、アナログ電話(電話も実は電話局から向こう側はデジタル伝送です)は8 [kHz]です。[3]A/D変換を行なうデバイス…A/Dコンバータアナログの世界の量である電圧をデジタルの量に変換するキーパーツと言えば、A/Dコンバータです。A/Dコンバータは、近年、軍用など特殊用途を除いてほぼすべてモノリシック(シリコンのかけら1個)化されており、電気釜から宇宙船までいろいろな場所で使われています。アナログ信号をデジタル値に変換する方法には、それだけで本が書けるほど多様な方法があり、目的とする信号によって、方法が異なります。ここでは、計測器に良く用いられ、直流に近い(=高速に時間変化しない)信号を高精度で変換できる二重積分形と呼ばれるものと、高速信号の変換に用いられる逐次比較形と呼ばれるものの原理をご説明します。 [4] 二重積分形A/Dコンバータの動作原理Fig.HJ0802_aは、二重積分形A/Dコンバータの概略構成です。ちょっと複雑ですが、信号の通る順を追って見て行けばさほど難しくありません。 | ||||||||||||||||||||||||||||||||||||||||||||||

Fig.HJ0802_a 二重積分形A/Dコンバータの構成 |

まず、入力信号はオペアンプの記号で示されている「積分器」という回路に入ります。この「積分」は数学の積分ですが、電気回路の積分はあまり難しく考える必要はありません。 入力は高速に変化しない>ので、ほとんど一定値を取ると考え、そのような信号を時間で積分すると、直線的に増加する一次関数になります(後で波形を調べます)。 積分された信号は、比較器(コンパレータ)に入り、GNDレベルと比較されます。ここからはロジック(論理)回路の世界です。 |

|||||||||||||||||||||||||||||||||||||||||||||

|

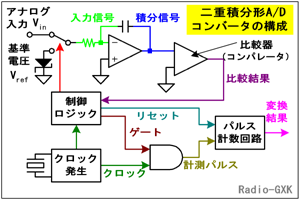

クロック発生回路は、常に一定周波数のクロックを発生しています。クロックは、制御ロジックとゲートに入りますが、制御ロジックは、クロックとコンパレータの入力から、積分器の入力切替(アナログ入力か基準電圧か)を行うのと、パルス計数回路にリセットを出すこと、それに、ゲート(ANDゲート)を開くタイミングを出力します。パルス計数回路は、リセットがかかってから、入ってきたパルスの数を数えます。 と、こう文章で書かれても動作は全く分かりません。そんな時は、Fig.HJ0802_bのようなタイミングチャートが役立ちます。 | ||||||||||||||||||||||||||||||||||||||||||||||

|

まず、話の都合上、スタート時点で積分器のコンデンサに溜まっている電荷はゼロ、すなわち積分器の出力はゼロから始まるとします。ここで、入力のスイッチが基準電圧から入力信号に切り替わった瞬間から話を始めます。 上にも書いたように、入力電圧の変化は緩やかで、ほとんど一定値V1とみなせるので、積分器の出力はどんどん上昇して行きます(区間A1)。 一定時間t0が経過すると、入力にあるスイッチが基準電圧源に切り替わり、入力と逆極性の定電圧Vrefが加わります。すると、積分器の出力は、符号が逆の積分なので、入力の傾きとは逆の傾きで降下してゆきます(区間B1)。 |

Fig.HJ0802_b A/Dコンバータのタイミング図 |

|||||||||||||||||||||||||||||||||||||||||||||

|

また、この時間中はゲートが開いており、クロックがパルス計数回路に加わります。 積分器の出力がゼロにまで降下した瞬間(ここでかかる時間をt1とします)、コンパレータの出力が反転して、制御ロジックはこれをきっかけに、入力のスイッチを再びアナログ入力側に切り替えると同時に、ゲートを閉じ、パルス計数回路の出力を確定した後、リセットします。パルス計数回路では、ゲートが開いていた時間内に出てきたクロック数n1をカウントして、デジタル値として出力します。 この図を見ると、積分器の出力は、入力の電圧(被測定電圧)を積分している時(区間A1)と、基準電圧を積分している時(区間B1)で、傾きの大きさが違います。 また、区間A1より低い電圧V2が入力されている時間(区間A2)は、その時間幅t0は制御ロジックが決めている同じt0なので、到達する積分値が低いのが分かります。 そして、区間B2で降下してゆく傾きは同じですからゼロ電圧に到達するのにかかる時間t2はt1より短くなります。従って、ゲートが開いている間(区間B2)に出てくるクロックの数n2もn1よりは少なくなります。 このようにして、アナログ電圧が、クロックの数としてデジタル値に変換されるわけです。 もっと、もっと分かりやすく説明すると… ・単位時間当たりにどれだけの水量V1が出てくるか分からない蛇口と、 ・出てきた水をためるバケツと、 ・一定水量V0で流し出すことのできるコックと、 ・水量がゼロになったことを検知するセンサーと、 ・水を流し出している時間を測るデジタル時計と、 ・デジタル時計やセンサーをモニタしながら蛇口やコックを制御する部分と、 を備えた装置であって、 ・蛇口から水の出るコックを開いて水を溜め、 ・時間t0(一定時間)経過したら水を止め、 ・流し出しコックを開いて溜まった水を捨て、 ・センサーの出力を見ながら、水量がゼロになるまでの時間t1を計測すれば、 ・t1の間に刻んだパルス数が蛇口から出てきた水量に比例する という原理で動作するコンバータ、ということになります(特許の請求項みたいになってしまいましたが)。 [5]逐次比較形A/Dコンバータの動作原理次に、逐次比較形A/Dコンバータの動作原理を簡単にご説明します。皆さんは、小学校の時に、上皿天秤で質量の分からないものを測定したことがありますか? 実はこの逐次比較形、という変換方式は、動作原理が上皿天秤での測定にそっくりなのです。ただ、分銅が1,2,5,10…[g]ではなくて、1,2,4,8,16,32…と2のべき乗のものがひとつずつしかないのが違いといえば違いです。上皿天秤での測定法を、どうやってエレキ回路で実現しているのでしょうか?まずはチップの中身を見て仕組みを考えます。逐次比較形の概略構造をFig.HJ0802_cに示します。上の二重積分形と同じく、少し複雑ですが、信号の流れとともに見て行きます(なお、これはA/Dコンバータの一例であり、実際にはもっと複雑です。理解のためのサンプルとお考え下さい)。 | ||||||||||||||||||||||||||||||||||||||||||||||

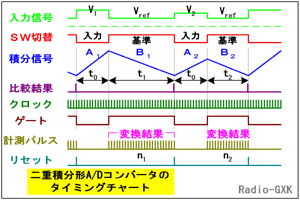

|

最初に、入ってきたところにある三角形は、「サンプルホールドアンプ(以下、S/Hアンプ、と書きます)」という特殊な信号処理です。二重積分形と異なり、常に激しく変化する信号を扱うことが多い逐次比較形では、変換を行っている間、入力の値が変化してしまっては困るので、普段はリアルタイムに入力に比例した出力を出しつつ(サンプル)も、タイミング信号でトリガがかかったら、(リセットが来るまで)その瞬間の電圧を保持し続ける(ホールド)というアンプです。 実は、このS/HアンプがA/Dコンバータの動的特性を握っているといっても過言ではないほど、高度な設計を必要とし、デバイスメーカのノウハウの塊です。 |

Fig.HJ0802_c 逐次比較形コンバータの概略構成 |

|||||||||||||||||||||||||||||||||||||||||||||

|

次の段は、コンパレータです。コンパレータは一方の入力がS/Hアンプの出力で、もう片方の入力が、D/Aコンバータの出力になっています。「なんでA/Dコンバータの中に反対の機能であるD/Aが入ってるんだ?」とお思いになるかと思いますが、説明はこの後でいたします。ともかく、コンパレータは「比較器」の名の通り、S/HアンプとD/Aの出力を比較して、S/Hアンプの出力の方が大きければ"1"を、D/Aの出力の方が大きければ"0"を出力します。 その次にある、逐次比較レジスタ(SAR=Successive Approximation Register)は、この後で説明するように順々に出てくるコンパレータの結果を格納しておくメモリのようなものです。その出力が変換結果になるわけですが、変換には何ステップも必要で、最終的な結果が出るまで、出てくる値は通常は利用しません。 D/Aコンバータは、逐次比較レジスタの出力を元に、アナログ電圧を出力します。例えば、上で書いたように4ビットのコンバータで、10 [mV]ステップであれば、逐次比較レジスタの出力が0110(10進数で6)であれば60 [mV]を、1110(10進数で14)であれば140 [mV]を出力します。 クロック発生器は、通常、外部からの変換入力に同期した内部のクロックを発生させて、ロジック系の動作に使います。また、制御ロジックは、S/Hアンプから逐次比較レジスタやD/A変換といった系のタイミングを発生させます。 ここまでで、各部の説明が終わりましたが、これではどうやって動作するのかまだサッパリ分かりません。そこで、再びタイミングチャートと、動作シーケンス表を用いてご説明します。ここでは、10 [mV]ステップの4ビットA/Dコンバータを例に取ります。これに、113 [mV]の電圧が入力されている場合を考えます。動作シーケンスを下の表で考えると… 「Comp」…比較器の出力で"0"か"1" 「SAR Out」…逐次比較レジスタの出力 「D/A出力」…D/Aコンバータの出力[mV] x…不定値又は前回/次回変換の値

説明が下手ですが、どうでしょうか? 80 [mV], 40 [mV], 20 [mV], 10 [mV]と大きな電圧から小さな電圧に順に加えて行き、入力より大きければ1を、小さければ0をSARのビットにセットしてゆくさまは、上皿天秤にこれらの分銅を乗せたりおろしたりしているように思えてきませんか? D/Aはこの「分銅」に相当するアナログ電圧を作り出すために必要だったわけです。 8ビット、12ビットとビット数を増やすには、分銅の種類を増やして、小さな分銅まで準備しておけばいい、ということになります。 | ||||||||||||||||||||||||||||||||||||||||||||||

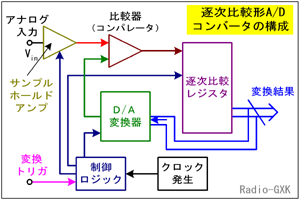

Fig.HJ0802_d 逐次比較形コンバータのタイミング |

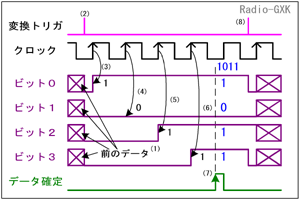

なお、上にも述べたように、分解能の10 [mV]に満たない3 [mV]はこのコンバータでは「切捨て」られます。 では最後に、この動作のタイミングチャートを見ておきましょう。これも一例で、市販品はもっと複雑です。(1)〜(7)の番号は、上の表の中の番号と対応しています。 逐次比較形は通常、変換トリガを入れてから、「変換終了」信号が出てくるまでのデータは不定で、使いません。変換終了信号を受け取ったCPU等が、バスをアクティブにしてA/Dコンバータから出てきた変換データを読み取ってメモリに格納する、という動作になります。 |

|||||||||||||||||||||||||||||||||||||||||||||

|

逐次比較形A/Dコンバータは、積分器を用いないため、一般に二重積分形よりも高速です。ビット数が増えると比例して時間がかかるので、20ビットや24ビットといった超高分解能のものはありません。大体16ビットまでです。速度的には、最近では構成に工夫が施され、14ビットでもサンプリング周波数が100 [MHz]を超えるようなものもざらにあります。このような高速コンバータは、レーダー、医療画像(CT等)、無線基地局などの分野で用いられています。 逐次比較形は、高速化は容易な一方、D/Aを含むので、回路規模は大きく複雑になります。 余談ですが、サンプリング周波数が100 [MHz]を超えるようになれば、HFなら受信した信号を高周波増幅して、ダイレクトにA/D変換してしまうことができます。こうして復調はデジタル信号処理で行うという、デジタル無線機も出てきているわけです。面倒な調整や局部発信器は要りませんし、非直線歪も発生しません。ソフトウェアで信号処理を変更することもできるので、今後も増えるでしょう。 それでは、解答に移ります。 A…アナログをデジタルですからA−D変換です B…2者を比較すれば構成が簡単なのは積分形です C…2者のうち高速なのは、逐次比較形です となりますから、正解は2と分かります。 | ||||||||||||||||||||||||||||||||||||||||||||||

|

|

|||||||||||||||||||||||||||||||||||||||||||||