| 仩 H20擭12寧婜 A-25 Code:[HJ0803] : 僒儞僾儖儂乕儖僪夞楬偺峑惓偲摦嶌尨棟 |

専嶕僒僀僩偐傜棃偨曽偼乧 柍慄岺妛偺婎慴 僩僢僾傊 埲壓傪僋儕僢僋偡傞偲丄尦偺儁乕僕偑峴偒愭偵旘傃丄偙偺僂僀儞僪僂偼暵偠傑偡 |

| 仭 柍慄岺妛傪妛傇 |

|

(1) 柍慄岺妛偺婎慴 |

|

擭搙暿弌戣堦棗 |

| H11擭 4寧婜,8寧婜,12寧婜 |

| H12擭 4寧婜,8寧婜,12寧婜 |

| H13擭 4寧婜,8寧婜,12寧婜 |

| H14擭 4寧婜,8寧婜,12寧婜 |

| H15擭 4寧婜,8寧婜,12寧婜 |

| H16擭 4寧婜,8寧婜,12寧婜 |

| H17擭 4寧婜,8寧婜,12寧婜 |

| H18擭 4寧婜,8寧婜,12寧婜 |

| H19擭 4寧婜,8寧婜,12寧婜 |

| H20擭 4寧婜,8寧婜,12寧婜 |

| H21擭 4寧婜,8寧婜,12寧婜 |

| H22擭 4寧婜,8寧婜,12寧婜 |

| H23擭 4寧婜,8寧婜,12寧婜 |

| H24擭 4寧婜,8寧婜,12寧婜 |

| H25擭 4寧婜,8寧婜,12寧婜 |

| H26擭 4寧婜,8寧婜,12寧婜 |

| H27擭 4寧婜,8寧婜,12寧婜 |

| H28擭 4寧婜,8寧婜,12寧婜 |

| H29擭 4寧婜,8寧婜,12寧婜 |

| H30擭 4寧婜,8寧婜,12寧婜 |

| R01擭 4寧婜,8寧婜,12寧婜 |

| R02擭 4寧婜,9寧婜,12寧婜 |

| R03擭 4寧婜,9寧婜,12寧婜 |

| R04擭 4寧婜,8寧婜,12寧婜 |

| R05擭 4寧婜,8寧婜,12寧婜 |

| R06擭 4寧婜,8寧婜,12寧婜 |

|

暘栰暿弌戣堦棗 |

| A 揹婥暔棟, B 揹婥夞楬 |

| C 擻摦慺巕, D 揹巕夞楬 |

| E 憲怣婡, F 庴怣婡 |

| G 揹尮, H 傾儞僥僫&媼揹慄 |

| I 揹攇揱斃, J 寁應 |

| 仭 僒僀僩億儕僔乕 |

| 仭 僒僀僩儅僢僾[1ama] |

| 仭 儕儞僋偲帒椏 |

仭 儊乕儖偼壓婰傑偱 |

|

| 2025擭 |

| 03/31 R06/12寧婜栤戣暸宖嵹 |

| 03/31 R06/08寧婜栤戣暸宖嵹 |

| 03/31 R06/04寧婜栤戣暸宖嵹 |

| 03/31 R05/12寧婜栤戣暸宖嵹 |

| 03/31 R05/08寧婜栤戣暸宖嵹 |

| 03/31 R05/04寧婜栤戣暸宖嵹 |

|

|

| |||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||

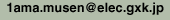

丂傾儅僠儏傾柍慄偺帋尡偱丄A/D僐儞僶乕僞偺撪晹夞楬傑偱弌戣偝傟傞偲偼巚偄傑偣傫偱偟偨偑丄擄偟偔峫偊偢丄僆儁傾儞僾夞楬偺墳梡偩偲巚偭偰丄夝愢傪撉傫偱傒偰壓偝偄丅乵侾乶僒儞僾儖儂乕儖僪夞楬偼偳偙偵巊傢傟丄栶妱偼壗偐丂傑偢丄偙偺僒儞僾儖儂乕儖僪夞楬偲屇偽傟傞夞楬偱偡偑丄偍側偠傒偩偲偄偆曽偼偦偆懡偔側偄偺偱偼側偄偱偟傚偆偐丠丂偦偙偱丄偳偙偱丄壗偺偨傔偵巊傢傟偰偄傞夞楬側偺偐傪挷傋偰偐傜丄偦偺摦嶌傪尒傞偙偲偵偟傑偟傚偆丅丂偙偺夞楬偼丄乽崗乆偲曄壔偡傞怣崋偺丄偁傞堦弖偺儗儀儖傪丄奜偐傜偺僩儕僈乕僞僀儈儞僌偵崌傢偣偰曐帩偡傞乿偲偄偆婡擻傪帩偪傑偡丅偪傚偆偳丄僇儊儔偱僔儍僢僞乕儃僞儞傪墴偡傛偆側姶偠偱偡丅偦偺偨傔丄偙偺婡擻傪昁梫偲偡傞怓乆側怣崋張棟偺応柺偵巊傢傟傑偡偑丄嵟傕傛偔梡偄傜傟偰偄傞偺偑丄A/D僐儞僶乕僞偺擖椡晹丄偦傟傕乽拃師斾妑宍乿偲屇偽傟傞A/D僐儞僶乕僞乮埲屻丄扨偵A/D偲婰偟傑偡乯偺僼儘儞僩僄儞僪偱偡丅 丂奆偝傫偼丄彫妛峑偺帪偵丄忋嶮揤攭偱幙検偺暘偐傜側偄傕偺傪應掕偟偨偙偲偑偁傝傑偡偐丠丂幚偼偙偺拃師斾妑宍丄偲偄偆曄姺曽幃偼丄摦嶌尨棟偑忋嶮揤攭偱偺應掕偵偦偭偔傝側偺偱偡丅偨偩丄暘摵偑1,2,5,10乧[g]偱偼側偔偰丄1,2,4,8,16,32乧偲2偺傋偒忔偺傕偺偑傂偲偮偢偮偟偐側偄偺偑堘偄偲偄偊偽堘偄偱偡丅忋嶮揤攭偱偺應掕朄傪丄偳偆傗偭偰僄儗僉夞楬偱幚尰偟偰偄傞偺偱偟傚偆偐丠 丂傑偢偼僠僢僾偺拞恎傪尒偰巇慻傒傪峫偊傑偡丅拃師斾妑宍偺奣棯峔憿傪Fig.HJ0803_a偵帵偟傑偡丅 | ||||||||||||||||||||||||||||||||||||||||||||||

|

丂怣崋偑擖偭偰偒偨偲偙傠偵偁傞偺偼丄忋偱愢柧偟偨傛偆側婡擻傪帩偮僒儞僾儖儂乕儖僪傾儞僾偱偡丅師偺抜偼丄僐儞僷儗乕僞偱偡丅僐儞僷儗乕僞偼堦曽偺擖椡偑S/H傾儞僾偺弌椡偱丄傕偆曅曽偺擖椡偑丄D/A僐儞僶乕僞偺弌椡偵側偭偰偄傑偡丅乽側傫偱A/D僐儞僶乕僞偺拞偵斀懳偺婡擻偱偁傞D/A偑擖偭偰傞傫偩丠乿偲偍巚偄偵側傞偐偲巚偄傑偡偑丄愢柧偼偙偺屻偱偄偨偟傑偡丅偲傕偐偔丄僐儞僷儗乕僞偼乽斾妑婍乿偺柤偺捠傝丄S/H傾儞僾偲D/A偺弌椡傪斾妑偟偰丄S/H傾儞僾偺弌椡偺曽偑戝偒偗傟偽"侾"傪丄D/A偺弌椡偺曽偑戝偒偗傟偽"侽"傪弌椡偟傑偡丅 |

Fig.HJ0803_a 拃師斾妑宍僐儞僶乕僞偺奣棯峔惉 |

|||||||||||||||||||||||||||||||||||||||||||||

|

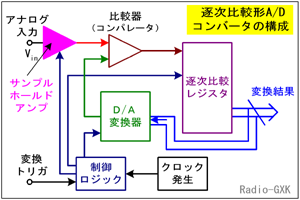

丂偦偺師偵偁傞丄拃師斾妑儗僕僗僞乮SAR=Successive Approximation Register乯偼丄偙偺屻偱愢柧偡傞傛偆偵弴乆偵弌偰偔傞僐儞僷儗乕僞偺寢壥傪奿擺偟偰偍偔儊儌儕偺傛偆側傕偺偱偡丅偦偺弌椡偑曄姺寢壥偵側傞傢偗偱偡偑丄曄姺偵偼壗僗僥僢僾傕昁梫偱丄嵟廔揑側寢壥偑弌傞傑偱丄弌偰偔傞抣偼捠忢偼棙梡偟傑偣傫丅 丂D/A僐儞僶乕僞偼丄拃師斾妑儗僕僗僞偺弌椡傪尦偵丄傾僫儘僌揹埑傪弌椡偟傑偡丅椺偊偽丄4價僢僩偺僐儞僶乕僞偱丄10 [mV]僗僥僢僾偱偁傟偽丄拃師斾妑儗僕僗僞偺弌椡偑0110乮10恑悢偱6乯偱偁傟偽60 [mV]傪丄1110乮10恑悢偱14乯偱偁傟偽140 [mV]傪弌椡偟傑偡丅 | ||||||||||||||||||||||||||||||||||||||||||||||

Fig.HJ0803_b 拃師斾妑宍僐儞僶乕僞偺僞僀儈儞僌 |

丂僋儘僢僋敪惗婍偼丄捠忢丄奜晹偐傜偺曄姺擖椡偵摨婜偟偨撪晹偺僋儘僢僋傪敪惗偝偣偰丄儘僕僢僋宯偺摦嶌偵巊偄傑偡丅傑偨丄惂屼儘僕僢僋偼丄S/H傾儞僾偐傜拃師斾妑儗僕僗僞傗D/A曄姺偲偄偭偨宯偺僞僀儈儞僌傪敪惗偝偣傑偡丅 丂偙偙傑偱偱丄奺晹偺愢柧偑廔傢傝傑偟偨偑丄偙傟偱偼偳偆傗偭偰摦嶌偡傞偺偐傑偩僒僢僷儕暘偐傝傑偣傫丅偦偙偱丄僞僀儈儞僌僠儍乕僩乮Fig.HJ0803_b乯偲丄摦嶌僔乕働儞僗昞傪梡偄偰偛愢柧偟傑偡丅偙偙偱偼丄10 [mV]僗僥僢僾偺4價僢僩A/D僐儞僶乕僞傪椺偵庢傝傑偡丅偙傟偵丄113 [mV]偺揹埑偑擖椡偝傟偰偄傞応崌傪峫偊傑偡丅摦嶌僔乕働儞僗傪壓偺昞偱峫偊傞偲乧 |

|||||||||||||||||||||||||||||||||||||||||||||

|

丂乽Comp乿乧斾妑婍偺弌椡偱"侽"偐"侾" 丂乽SAR Out乿乧拃師斾妑儗僕僗僞偺弌椡 丂乽D/A弌椡乿乧D/A僐儞僶乕僞偺弌椡[mV] 丂x乧晄掕抣枖偼慜夞/師夞曄姺偺抣

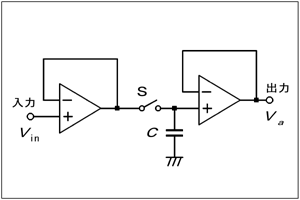

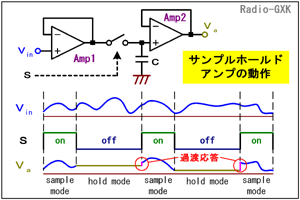

丂愢柧偑壓庤偱偡偑丄偳偆偱偟傚偆偐丠 80 [mV], 40 [mV], 20 [mV], 10 [mV]偲戝偒側揹埑偐傜彫偝側揹埑偵弴偵壛偊偰峴偒丄擖椡傛傝戝偒偗傟偽侾傪丄彫偝偗傟偽侽傪SAR偺價僢僩偵僙僢僩偟偰備偔偝傑偼丄忋嶮揤攭偵偙傟傜偺暘摵傪忔偣偨傝偍傠偟偨傝偟偰偄傞傛偆偵巚偊偰偒傑偣傫偐丠丂D/A偼偙偺乽暘摵乿偵憡摉偡傞傾僫儘僌揹埑傪嶌傝弌偡偨傔偵昁梫偩偭偨傢偗偱偡丅 丂8價僢僩丄12價僢僩偲價僢僩悢傪憹傗偡偵偼丄暘摵偺庬椶傪憹傗偟偰丄彫偝側暘摵傑偱弨旛偟偰偍偗偽偄偄丄偲偄偆偙偲偵側傝傑偡丅 丂偦傟偱偼壗屘丄僒儞僾儖儂乕儖僪夞楬偑昁梫側偺偱偟傚偆偐丠丂傕偟丄偙偺夞楬偑側偄偲偡傞偲丄Fig.HJ0803_a偱A/D偺擖椡偲僐儞僷儗乕僞偑捈寢偵側傝傑偡丅擖椡偼愨偊偢曄壔偟偰偄傞怣崋偱偡偐傜丄忋嶮揤攭偺乽應傞傕偺傪嵹偣偰偄傞乿懁偺廳偝偑曄壔偟偰偟傑偆偙偲偵側傝丄偙傟偱偼應傟傑偣傫丅偮傑傝丄堦夞偺僔乕働儞僗偑夢傞傑偱偼丄擖椡偺怣崋偼惷巭偟偰偄偰偔傟側偗傟偽側傜側偄偺偱丄僒儞僾儖儂乕儖僪夞楬偑昁梫偵側傞偺偱偡丅 乵俀乶僒儞僾儖儂乕儖僪夞楬偺摦嶌丂僒儞僾儖儂乕儖僪夞楬偼丄乽僒儞僾儖儌乕僪乿偲乽儂乕儖僪儌乕僪乿偲屇偽傟傞2偮偺摦嶌儌乕僪傪桳偟傑偡丅埲壓丄Fig.HJ0803_c偺夞楬恾偲僞僀儈儞僌僠儍乕僩傪婎偵峫偊傑偡丅 | ||||||||||||||||||||||||||||||||||||||||||||||

Fig.HJ0803_c 僒儞僾儖儂乕儖僪傾儞僾偺峔惉偲摦嶌 |

(1) 僒儞僾儖儌乕僪 丂僒儞僾儖儌乕僪偱偼丄僗僀僢僠俽偺惂屼偼ON偵偟傑偡丅偡傞偲丄Amp1偼棙摼亄1偺憹暆夞楬偱偡偐傜丄偦偺弌椡偼僐儞僨儞僒俠傪廩曻揹偟側偑傜丄擖椡怣崋倁in偲摨偠偵曄壔偟丄Amp2偺擖椡偵擖傝傑偡丅Amp2傕棙摼偑亄1偺憹暆夞楬偱偡偐傜丄寢嬊丄弌椡倁a偵偼擖椡抂巕倁in偲慡偔摨偠攇宍偑尰傟傑偡丅 (2) 儂乕儖僪儌乕僪 丂儂乕儖僪儌乕僪偱偼丄僗僀僢僠俽偺惂屼傪OFF偵偟傑偡丅偡傞偲丄Amp1偲Amp2偼愗傝棧偝傟傑偡偑丄俠偵棴傑偭偨揹壸偵傛偭偰丄Amp2偺旕斀揮擖椡抂巕偵偼俽偑愗傟傞捈慜偺揹埵偑妡偐傝懕偗傑偡丅 |

|||||||||||||||||||||||||||||||||||||||||||||

|

丂僆儁傾儞僾偺儌僨儖偺拞偵乽擖椡僀儞僺乕僟儞僗偑柍尷戝乿偲偄偆忦審偑偁偭偨偺傪巚偄弌偟偰偄偨偩偒偨偄偺偱偡偑丄Amp2偺旕斀揮擖椡抂巕偺擖椡僀儞僺乕僟儞僗偑柍尷戝偱偁傞尷傝丄俠偼曻揹偣偢丄俽偑OFF偵側偭偰偄傞娫偼丄弌椡倁a偵偼丄俽偑OFF偵側偭偨弖娫偺揹埑偑弌懕偗傑偡丅 丂傕偪傠傫丄尰幚偺悽奅偱偼偙傫側棟憐揑側偙偲偼偁傝傑偣傫丅僆儁傾儞僾偺擖椡抂巕偼丄僶僀傾僗揹棳偲偄偆0偱側偄揹棳偑棳傟崬傫偩傝棳傟弌偨傝偟傑偡偟丄僐儞僨儞僒偵傕楻傟揹棳偑偁傝丄揹壸偼帪娫偲偲傕偵曄壔偟傑偡丅偦傟偵偮傟偰丄僐儞僨儞僒椉抂偺揹埑傕曄壔偡傞偺偱丄倁a偼儂乕儖僪儌乕僪偱偼柍尷偵堦掕偺抣偱偼桳傝摼傑偣傫丅 丂偟偐偟丄捠忢丄拃師斾妑宍偺僐儞僶乕僞偺応崌丄曄姺帪娫偑悢[兪s]乣悢10[ns]偲抁偄偨傔丄偙偺帪娫撪偵1LSB暘偺暘夝擻偵斾傋偰柍帇偱偒傞戝偒偝偺曄摦偱偁傟偽丄曄姺寢壥偵塭嬁偑側偄偨傔丄僒儞僾儖儂乕儖僪傾儞僾偼懚嵼壙抣偑偁傞偺偱偡丅 乵俁乶僒儞僾儖儂乕儖僪傾儞僾偺夞楬愝寁偺梫揰丂忋偵彂偄偨傛偆側丄僶僀傾僗揹棳傗僐儞僨儞僒偺楻傟揹棳傪嬌椡彫偝偔偡傞偙偲傕梫揰偺堦偮偱偡丅傕偆堦偮廳梫側偺偼丄儂乕儖僪儌乕僪偐傜僒儞僾儖儌乕僪偵慗堏偡傞乮俽傪OFF仺ON偵偡傞乯帪偺丄夁搉墳摎偱偡丅Fig.HJ0803_c偱偄偆偲丄愒娵偱埻傫偩晹暘偺偙偲偱偡丅丂俽偑OFF偵側偭偰偄傞娫傕丄Amp1偺弌椡偼忢偵倁in偵捛悘偟偰偄傑偡偑丄僐儞僨儞僒偺椉抂揹埑偼慜偺揹埑傪曐帩偟偰偄傞偨傔丄僗僀僢僠偑ON偵側偭偨弖娫丄椉幰偺揹埑偼堦抳偟傑偣傫丅Amp1偼戝媫偓偱俠偵揹棳傪棳偟崬傫偩傝丄媧偄弌偟偨傝偟偰丄帺暘偺弌椡揹埑偲俠偺椉抂揹埑傪崌抳偝偣傛偆偲摥偒傑偡丅 丂偲偙傠偑丄Amp1偺揹棳嬱摦擻椡偑懌傝側偐偭偨傝丄俠偑戝偒夁偓偨傝丄Amp1偺埵憡梋桾偑晄懌乮敪怳偟傗偡偄偙偲乯偟偰偄偨傝偡傞偲丄Amp1偺弌椡偲倁in偑堦抳偡傞偺偵戝曄挿偄帪娫偑妡偐偭偨傝丄帪娫撪偵堦抳偟側偐偭偨傝偟傑偡丅偡傞偲丄俽偑OFF偵側傞弖娫傕倁in偲俠偺椉抂偑堎側偭偨揹埑偵側偭偨忬懺偱曄姺偑奐巒偝傟傞偙偲偵側傞偺偱丄曄姺寢壥偺岆嵎偵側偭偰尰傟傑偡丅 丂傑偨丄曄姺傪崅懍偵峴側偆偨傔偵偼丄拃師斾妑儘僕僢僋帺懱偺崅懍壔傕昁梫偱偡偑丄僒儞僾儖儌乕僪傪偄偐偵抁帪娫偱廔椆偝偣傞偐丄傕壽戣偲側傝傑偡丅僒儞僾儖儌乕僪偵慗堏偟偰偐傜崅懍偵捛悘偟偰偔傟傟偽偔傟傞傎偳丄憗偔曄姺傪奐巒偱偒傞傢偗偱偡偐傜丅 偦傟偱偼丄夝摎偵堏傝傑偡丅 丂俙乧俠偵偼俽偑抐(OFF)偵側傞捈慜偺揹埑偑曐帩偝傟傑偡 丂俛乧僒儞僾儕儞僌偼俽偑愙(ON)偺忬懺偱峴側傢傟傑偡 丂俠乧俠偺廩曻揹偼丄擖椡傛傝廫暘抁偄帪娫偱峴側傢傟側偗傟偽側傝傑偣傫 偲側傝傑偡偐傜丄惓夝偼俆偲暘偐傝傑偡丅 | ||||||||||||||||||||||||||||||||||||||||||||||

|

|

|||||||||||||||||||||||||||||||||||||||||||||